Professional Documents

Culture Documents

Computer Architecture 3rd Edition by Moris Mano CH 05

Uploaded by

Sadaf RasheedOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Computer Architecture 3rd Edition by Moris Mano CH 05

Uploaded by

Sadaf RasheedCopyright:

Available Formats

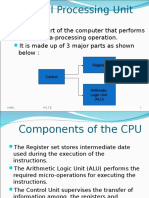

Basic Computer Organization & Design

BASIC COMPUTER ORGANIZATION AND DESIGN

Instruction Codes

Computer Registers

Computer Instructions

Timing and Control

Instruction Cycle

Memory Reference Instructions

Input-Output and Interrupt

Complete Computer Description

Design of Basic Computer

Design of Accumulator Logic

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

Instruction codes

INSTRUCTION CODES

Program:

A set of instructions that specify the operations, operands, and the

sequence by which processing has to occur.

Instruction Code:

A group of bits that tell the computer to perform

a specific operation (a sequence of micro-operation)

-->macro-operation

- usually divided into operation code, operand

address, addressing mode, etc.

- basic addressing modes

Immediate, Direct, Indirect

Simplest stored program organization

15

12 11

Opcode

Address

Instruction Format

15

0

Binary Operand

Memory

4096x16

Instructions

(program)

Operands

(data)

Processor register

(Accumulator, AC)

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

Instruction codes

INDIRECT ADDRESS

Instruction Format

15 14

12 11

Address

I Opcode

Indirect address

Direct Address

22

0 ADD

457

35

300

457

1 ADD

300

1350

Operand

1350

Operand

AC

AC

Effective Address(EFA, EA)

The address, that can be directly used without modification to access

an operand for a computation-type instruction, or as the target

address for a branch-type instruction

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

Registers

COMPUTER REGISTERS

Registers in the Basic Computer

11

PC

11

Memory

AR

15

4096 x 16

IR

15

15

TR

7

OUTR

DR

7

15

INPR

AC

List of BC Registers

DR

AR

AC

IR

PC

TR

INPR

OUTR

16

12

16

16

12

16

8

8

Computer Organization

Data Register

Holds memory operand

Address Register

Holds address for memory

Accumulator

Processor register

Instruction Register Holds instruction code

Program Counter

Holds address of instruction

Temporary Register Holds temporary data

Input Register

Holds input character

Output Register

Holds output character

Computer Architectures Lab

Basic Computer Organization & Design

Registers

COMMON BUS SYSTEM

S2

S1

S0

Memory unit

4096 x 16

Write

Bus

7

Address

Read

AR

LD INR CLR

PC

LD INR CLR

DR

LD INR CLR

Adder

and

logic

AC

LD INR CLR

INPR

IR

TR

LD

LD INR CLR

OUTR

LD

16-bit common bus

Computer Organization

Clock

Computer Architectures Lab

Basic Computer Organization & Design

Instructions

COMPUTER(BC) INSTRUCTIONS

Basic Computer Instruction code format

Memory-Reference Instructions

15

I

14

12 11

Opcode

0

Address

Register-Reference Instructions

15

0

12 11

Register operation

1

Input-Output Instructions

15

1 1

Computer Organization

12 11

1

(OP-code = 000 ~ 110)

(OP-code = 111, I = 0)

0

(OP-code =111, I = 1)

0

I/O operation

Computer Architectures Lab

Basic Computer Organization & Design

Instructions

BASIC COMPUTER INSTRUCTIONS

Symbol

AND

ADD

LDA

STA

BUN

BSA

ISZ

Hex Code

I=0

I=1

0xxx 8xxx

1xxx 9xxx

2xxx Axxx

3xxx Bxxx

4xxx Cxxx

5xxx

Dxxx

6xxx

Exxx

Description

AND memory word to AC

Add memory word to AC

Load AC from memory

Store content of AC into memory

Branch unconditionally

Branch and save return address

Increment and skip if zero

CLA

CLE

CMA

CME

CIR

CIL

INC

SPA

SNA

SZA

SZE

HLT

7800

7400

7200

7100

7080

7040

7020

7010

7008

7004

7002

7001

Clear AC

Clear E

Complement AC

Complement E

Circulate right AC and E

Circulate left AC and E

Increment AC

Skip next instr. if AC is positive

Skip next instr. if AC is negative

Skip next instr. if AC is zero

Skip next instr. if E is zero

Halt computer

INP

OUT

SKI

SKO

ION

IOF

F800

F400

F200

F100

F080

F040

Input character to AC

Output character from AC

Skip on input flag

Skip on output flag

Interrupt on

Interrupt off

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

Instructions

INSTRUCTION SET COMPLETENESS

A computer should have a set of instructions so that the user can

construct machine language programs to evaluate any function that is

known to be computable.

Instruction Types

Functional Instructions

- Arithmetic, logic, and shift instructions

- ADD, CMA, INC, CIR, CIL, AND, CLA

Transfer Instructions

- Data transfers between the main memory

and the processor registers

- LDA, STA

Control Instructions

- Program sequencing and control

- BUN, BSA, ISZ

Input/Output Instructions

- Input and output

- INP, OUT

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

Timing and control

TIMING AND CONTROL

Control unit of basic computer

15

Instruction register (IR)

14 13 12

11 - 0

Other inputs

3x8

decoder

7 6543 210

D0

Control

logic

gates

D7

Control

outputs

T15

T0

15 14 . . . . 2 1 0

4 x 16

decoder

4-bit

sequence

counter

(SC)

Increment (INR)

Clear (CLR)

Clock

Control unit implementation

Hardwired Implementation

Microprogrammed Implementation

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

10

Timing and control

TIMING

SIGNALS

- Generated by 4-bit sequence counter and 4x16 decoder

- The SC can be incremented or cleared.

- Example: T0, T1, T2, T3, T4, T0, T1, . . .

Assume: At time T4, SC is cleared to 0 if decoder output D3 is active.

D3T4: SC 0

Clock

T0

T1

T2

T3

T4

T0

T0

T1

T2

T3

T4

D3

CLR

SC

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

11

Instruction Cycle

INSTRUCTION CYCLE

BC Instruction cycle: [Fetch Decode [Indirect] Execute]*

Fetch and Decode

T0: AR PC (S0S1S2=010, T0=1)

T1: IR M [AR], PC PC + 1 (S0S1S2=111, T1=1)

T2: D0, . . . , D7 Decode IR(12-14), AR IR(0-11), I IR(15)

T1

S2

T0

S1 Bus

S0

Memory

unit

7

Address

Read

AR

LD

PC

INR

IR

LD

5

Clock

Common bus

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

12

Instrction Cycle

DETERMINE THE TYPE OF INSTRUCTION

Start

SC

AR PC

T0

IR M[AR], PC PC + 1

T1

T2

Decode Opcode in IR(12-14),

AR IR(0-11), I IR(15)

(Register or I/O) = 1

(I/O) = 1

I

T3

Execute

input-output

instruction

SC 0

D'7IT3:

D'7I'T3:

D7I'T3:

D7IT3:

D7

= 0 (Memory-reference)

= 0 (register)

(indirect) = 1

T3

Execute

register-reference

instruction

SC 0

T3

AR M[AR]

= 0 (direct)

T3

Nothing

Execute

memory-reference

instruction

SC 0

T4

AR M[AR]

Nothing

Execute a register-reference instr.

Execute an input-output instr.

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

13

Instruction Cycle

REGISTER REFERENCE INSTRUCTIONS

Register Reference Instructions are identified when

- D7 = 1, I = 0

- Register Ref. Instr. is specified in b0 ~ b11 of IR

- Execution starts with timing signal T3

r = D7 I T3 => Register Reference Instruction

Bi = IR(i) , i=0,1,2,...,11

CLA

CLE

CMA

CME

CIR

CIL

INC

SPA

SNA

SZA

SZE

HLT

r:

rB11:

rB10:

rB9:

rB8:

rB7:

rB6:

rB5:

rB4:

rB3:

rB2:

rB1:

rB0:

Computer Organization

SC 0

AC 0

E0

AC AC

E E

AC shr AC, AC(15) E, E AC(0)

AC shl AC, AC(0) E, E AC(15)

AC AC + 1

if (AC(15) = 0) then (PC PC+1)

if (AC(15) = 1) then (PC PC+1)

if (AC = 0) then (PC PC+1)

if (E = 0) then (PC PC+1)

S 0 (S is a start-stop flip-flop)

Computer Architectures Lab

Basic Computer Organization & Design

14

MR Instructions

MEMORY REFERENCE INSTRUCTIONS

Symbol

AND

ADD

LDA

STA

BUN

BSA

ISZ

Operation

Decoder

D0

D1

D2

D3

D4

D5

D6

Symbolic Description

AC AC M[AR]

AC AC + M[AR], E Cout

AC M[AR]

M[AR] AC

PC AR

M[AR] PC, PC AR + 1

M[AR] M[AR] + 1, if M[AR] + 1 = 0 then PC PC+1

- The effective address of the instruction is in AR and was placed there during

timing signal T2 when I = 0, or during timing signal T3 when I = 1

- Memory cycle is assumed to be short enough to complete in a CPU cycle

- The execution of MR Instruction starts with T4

AND to AC

D0T4:

D0T5:

ADD to AC

D1T4:

D1T5:

DR M[AR]

AC AC DR, SC 0

Read operand

AND with AC

DR M[AR]

AC AC + DR, E Cout, SC 0

Read operand

Add to AC and store carry in E

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

15

MEMORY REFERENCE INSTRUCTIONS

LDA: Load to AC

D2T4: DR M[AR]

D2T5: AC DR, SC 0

STA: Store AC

D3T4: M[AR] AC, SC 0

BUN: Branch Unconditionally

D4T4: PC AR, SC 0

BSA: Branch and Save Return Address

M[AR] PC, PC AR + 1

Memory, PC, AR at time T4

20

PC = 21

BSA

135

Next instruction

AR = 135

136

Subroutine

BUN

Memory

Computer Organization

135

Memory, PC after execution

20

BSA

135

21

Next instruction

135

21

Subroutine

PC = 136

BUN

135

Memory

Computer Architectures Lab

Basic Computer Organization & Design

16

MR Instructions

MEMORY REFERENCE INSTRUCTIONS

BSA:

D5T4:

D5T5:

M[AR] PC, AR AR + 1

PC AR, SC 0

ISZ: Increment and Skip-if-Zero

D6T4: DR M[AR]

D6T5: DR DR + 1

D6T4: M[AR] DR, if (DR = 0) then (PC PC + 1), SC 0

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

17

MR Instructions

FLOWCHART FOR MEMORY REFERENCE INSTRUCTIONS

Memory-reference instruction

AND

ADD

D0 T 4

DR <- M[AR]

LDA

D1 T 4

DR <- M[AR]

D0 T 5

D1 T 5

AC <- AC DR

AC <- AC + DR

SC <- 0

E <- Cout

SC <- 0

BUN

BSA

D4 T 4

PC <- AR

SC <- 0

D2 T 4

D 3T 4

M[AR] <- AC

SC <- 0

DR <- M[AR]

D2 T 5

AC <- DR

SC <- 0

ISZ

D5 T 4

M[AR] <- PC

AR <- AR + 1

D5 T 5

PC <- AR

SC <- 0

STA

D6 T 4

DR <- M[AR]

D6 T 5

DR <- DR + 1

D6 T 6

M[AR] <- DR

If (DR = 0)

then (PC <- PC + 1)

SC <- 0

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

18

I/O and Interrupt

INPUT-OUTPUT AND INTERRUPT

A Terminal with a keyboard and a Printer

Input-Output Configuration

Input-output

terminal

Printer

Serial

communication

interface

registers and

Computer

flip-flops

Receiver

interface

OUTR

FGO

AC

INPR

OUTR

FGI

FGO

IEN

Input register - 8 bits

Output register - 8 bits

Input flag - 1 bit

Output flag - 1 bit

Interrupt enable - 1 bit

Keyboard

Transmitter

interface

INPR

FGI

Serial Communications Path

Parallel Communications Path

- The terminal sends and receives serial information

- The serial info. from the keyboard is shifted into INPR

- The serial info. for the printer is stored in the OUTR

- INPR and OUTR communicate with the terminal

serially and with the AC in parallel.

- The flags are needed to synchronize the timing

difference between I/O device and the computer

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

19

I/O and Interrupt

PROGRAM CONTROLLED DATA TRANSFER

-- CPU --

-- I/O Device --

/* Input */

/* Initially FGI = 0 */

loop: If FGI = 0 goto loop

AC INPR, FGI 0

loop: If FGI = 1 goto loop

/* Output */

/* Initially FGO = 1 */

loop: If FGO = 0 goto loop

OUTR AC, FGO 0

loop: If FGO = 1 goto loop

INPR new data, FGI

consume OUTR, FGO 1

FGI=0

FGO=1

Start Input

Start Output

FGI 0

yes

FGI=0

AC Data

yes

no

More

Character

no

END

Computer Organization

FGO=0

no

AC INPR

yes

OUTR AC

FGO 0

yes

More

Character

no

END

Computer Architectures Lab

Basic Computer Organization & Design

20

INPUT-OUTPUT INSTRUCTIONS

D7IT3 = p

IR(i) = Bi, i = 6, , 11

INP

OUT

SKI

SKO

ION

IOF

pB11:

pB10:

pB9:

pB8:

pB7:

pB6:

Computer Organization

AC(0-7) INPR, FGI 0

OUTR AC(0-7), FGO 0

if(FGI = 1) then (PC PC + 1)

if(FGO = 1) then (PC PC + 1)

IEN 1

IEN 0

Input char. to AC

Output char. from AC

Skip on input flag

Skip on output flag

Interrupt enable on

Interrupt enable off

Computer Architectures Lab

Basic Computer Organization & Design

21

I/O and Interrupt

PROGRAM-CONTROLLED INPUT/OUTPUT

Program-controlled I/O

- Continuous CPU involvement

I/O takes valuable CPU time

- CPU slowed down to I/O speed

- Simple

- Least hardware

Input

LOOP,

SKI DEV

BUN LOOP

INP DEV

Output

LOOP,

LOP,

LD

SKO

BUN

OUT

Computer Organization

DATA

DEV

LOP

DEV

Computer Architectures Lab

Basic Computer Organization & Design

22

INTERRUPT INITIATED INPUT/OUTPUT

- Open communication only when some data has to be passed --> interrupt.

- The I/O interface, instead of the CPU, monitors the I/O device.

- When the interface founds that the I/O device is ready for data transfer,

it generates an interrupt request to the CPU

- Upon detecting an interrupt, the CPU stops momentarily the task

it is doing, branches to the service routine to process the data

transfer, and then returns to the task it was performing.

* IEN (Interrupt-enable flip-flop)

- can be set and cleared by instructions

- when cleared, the computer cannot be interrupted

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

23

I/O and Interrupt

FLOWCHART FOR INTERRUPT CYCLE

R = Interrupt f/f

Instruction cycle

=0

IEN

=1

=1

=1

=1

Interrupt cycle

Store return address

in location 0

M[0] <- PC

Fetch and decode

instructions

Execute

instructions

=0

Branch to location 1

PC <- 1

FGI

=0

FGO

=0

IEN <- 0

R <- 0

R <- 1

- The interrupt cycle is a HW implementation of a branch

and save return address operation.

- At the beginning of the next instruction cycle, the

instruction that is read from memory is in address 1.

- At memory address 1, the programmer must store a branch instruction

that sends the control to an interrupt service routine

- The instruction that returns the control to the original

program is "indirect BUN 0"

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

24

I/O and Interrupt

REGISTER TRANSFER OPERATIONS IN INTERRUPT CYCLE

Memory

Before interrupt

0

1

BUN

1120

Main

Program

255

PC = 256

1120

After interrupt cycle

0

PC = 1 0

Main

Program

255

256

1120

I/O

Program

1

BUN

256

BUN

1120

I/O

Program

0

BUN

Register Transfer Statements for Interrupt Cycle

- R F/F 1 if IEN (FGI + FGO)T0T1T2

T0T1T2 (IEN)(FGI + FGO): R 1

- The fetch and decode phases of the instruction cycle

must be modified:Replace T0, T1, T2 with R'T0, R'T1, R'T2

- The interrupt cycle :

RT0: AR 0, TR PC

RT1:

M[AR] TR, PC 0

RT2:

PC PC + 1, IEN 0, R 0, SC 0

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

25

I/O and Interrupt

FURTHER QUESTIONS ON INTERRUPT

Questions on Interrupt

How can the CPU recognize the device

requesting an interrupt ?

Since different devices are likely to require

different interrupt service routines, how can

the CPU obtain the starting address of the

appropriate routine in each case ?

Should any device be allowed to interrupt the

CPU while another interrupt is being serviced ?

How can the situation be handled when two or

more interrupt requests occur simultaneously ?

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

26

Description

COMPLETE COMPUTER DESCRIPTION

Flowchart of Operations

start

SC <- 0, IEN <- 0, R <- 0

=0(Instruction

R

Cycle)

RT0

AR <- PC

RT1

IR <- M[AR], PC <- PC + 1

RT2

AR <- IR(0~11), I <- IR(15)

D0...D7 <- Decode IR(12 ~ 14)

=1(Register or I/O)

=1 (I/O)

D7IT3

Execute

I/O

Instruction

=0 (Register)

D7IT3

Execute

RR

Instruction

D7

=1(Interrupt

Cycle)

RT0

AR <- 0, TR <- PC

RT1

M[AR] <- TR, PC <- 0

RT2

PC <- PC + 1, IEN <- 0

R <- 0, SC <- 0

=0(Memory Ref)

=1(Indir)

D7IT3

AR <- M[AR]

=0(Dir)

D7IT3

Idle

Execute MR

Instruction

Computer Organization

D7T4

Computer Architectures Lab

Basic Computer Organization & Design

27

Description

COMPLETE COMPUTER DESCRIPTION

Microoperations

Fetch

Decode

RT0:

RT1:

RT2:

Indirect

D7IT3:

Interrupt

T0T1T2(IEN)(FGI + FGO):

RT0:

RT1:

RT2:

Memory-Reference

AND

D0T4:

D0T5:

ADD

D1T4:

D1T5:

LDA

D2T4:

D2T5:

STA

D3T4:

BUN

D4T4:

BSA

D5T4:

D5T5:

ISZ

D6T4:

D6T5:

D6T6:

Computer Organization

AR <- PC

IR <- M[AR], PC <- PC + 1

D0, ..., D7 <- Decode IR(12 ~ 14),

AR <- IR(0 ~ 11), I <- IR(15)

AR <- M[AR]

R <- 1

AR <- 0, TR <- PC

M[AR] <- TR, PC <- 0

PC <- PC + 1, IEN <- 0, R <- 0, SC <- 0

DR <- M[AR]

AC <- AC . DR, SC <- 0

DR <- M[AR]

AC <- AC + DR, E <- Cout, SC <- 0

DR <- M[AR]

AC <- DR, SC <- 0

M[AR] <- AC, SC <- 0

PC <- AR, SC <- 0

M[AR] <- PC, AR <- AR + 1

PC <- AR, SC <- 0

DR <- M[AR]

DR <- DR + 1

M[AR] <- DR, if(DR=0) then (PC <- PC + 1),

SC <- 0

Computer Architectures Lab

Basic Computer Organization & Design

28

Description

COMPLETE COMPUTER DESCRIPTION

Microoperations

Register-Reference

D7IT3 = r

IR(i) = Bi

r:

CLA

rB11:

CLE

rB10:

CMA

rB9:

CME

rB8:

CIR

rB7:

CIL

rB6:

INC

rB5:

SPA

rB4:

SNA

rB3:

SZA

rB2:

SZE

rB1:

HLT

rB0:

Input-Output

INP

OUT

SKI

SKO

ION

IOF

Computer Organization

D7IT3 = p

IR(i) = Bi

p:

pB11:

pB10:

pB9:

pB8:

pB7:

pB6:

(Common to all register-reference instr)

(i = 0,1,2, ..., 11)

SC <- 0

AC <- 0

E <- 0

AC <- AC

E <- E

AC <- shr AC, AC(15) <- E, E <- AC(0)

AC <- shl AC, AC(0) <- E, E <- AC(15)

AC <- AC + 1

If(AC(15) =0) then (PC <- PC + 1)

If(AC(15) =1) then (PC <- PC + 1)

If(AC = 0) then (PC <- PC + 1)

If(E=0) then (PC <- PC + 1)

S <- 0

(Common to all input-output instructions)

(i = 6,7,8,9,10,11)

SC <- 0

AC(0-7) <- INPR, FGI <- 0

OUTR <- AC(0-7), FGO <- 0

If(FGI=1) then (PC <- PC + 1)

If(FGO=1) then (PC <- PC + 1)

IEN <- 1

IEN <- 0

Computer Architectures Lab

Basic Computer Organization & Design

29

Design of Basic Computer

DESIGN OF BASIC COMPUTER(BC)

Hardware Components of BC

A memory unit: 4096 x 16.

Registers:

AR, PC, DR, AC, IR, TR, OUTR, INPR, and SC

Flip-Flops(Status):

I, S, E, R, IEN, FGI, and FGO

Decoders:

a 3x8 Opcode decoder

a 4x16 timing decoder

Common bus: 16 bits

Control logic gates:

Adder and Logic circuit: Connected to AC

Control Logic Gates

- Input Controls of the nine registers

- Read and Write Controls of memory

- Set, Clear, or Complement Controls of the flip-flops

- S2, S1, S0 Controls to select a register for the bus

- AC, and Adder and Logic circuit

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

30

Design of Basic Computer

CONTROL OF REGISTERS AND MEMORY

Address Register; AR

Scan all of the register transfer statements that change the content of AR:

RT0:

AR PC

LD(AR)

RT2:

AR IR(0-11) LD(AR)

D7IT3: AR M[AR]

LD(AR)

RT0:

AR 0

CLR(AR)

D5T4: AR AR + 1

INR(AR)

LD(AR) = R'T0 + R'T2 + D'7IT3

CLR(AR) = RT0

INR(AR) = D5T4

T2

D'7

I

T3

From bus

12

12

AR

To bus

Clock

LD

INR

CLR

R

T0

D

T4

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

31

Design of Basic Computer

CONTROL OF FLAGS

IEN: Interrupt Enable Flag

pB7: IEN 1 (I/O Instruction)

pB6: IEN 0 (I/O Instruction)

RT2: IEN 0 (Interrupt)

p = D7IT3 (Input/Output Instruction)

D

I

T3

p

B7

B6

IEN

R

T2

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

32

Design of Basic Computer

CONTROL OF COMMON BUS

x1

x2

x3

x4

x5

x6

x7

S2

Encoder

S1

S0

x1 x2 x3 x4 x5 x6 x7

0

1

0

0

0

0

0

0

For AR

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

S2 S1 S0

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Multiplexer

bus select

inputs

selected

register

none

AR

PC

DR

AC

IR

TR

Memory

D4T4: PC AR

D5T5: PC AR

x1 = D4T4 + D5T5

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

33

Design of AC Logic

DESIGN OF ACCUMULATOR LOGIC

Circuits associated with AC

From DR

From INPR

16

16

8

Adder and

logic

circuit

16

16

AC

To bus

LD

INR

CLR

Clock

Control

gates

All the statements that change the content of AC

D0T5:

D1T5:

D2T5:

pB11:

rB9:

rB7 :

rB6 :

rB11 :

rB5 :

AC AC DR

AND with DR

AC AC + DR

Add with DR

AC DR

Transfer from DR

AC(0-7) INPR

Transfer from INPR

AC AC

Complement

AC shr AC, AC(15) E Shift right

AC shl AC, AC(0) E

Shift left

AC 0

Clear

AC AC + 1

Increment

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

34

Design of AC Logic

CONTROL OF AC REGISTER

Gate structures for controlling

the LD, INR, and CLR of AC

From Adder

and Logic

D0

T5

D1

AND

D2

T5

p

B11

r

B9

DR

B7

B6

B5

ADD

16

16

AC

To bus

Clock

LD

INR

CLR

INPR

COM

SHR

SHL

INC

CLR

B11

Computer Organization

Computer Architectures Lab

Basic Computer Organization & Design

35

Design of AC Logic

ADDER AND LOGIC CIRCUIT

One stage of Adder and Logic circuit

DR(i)

AC(i)

AND

Ci

Ii

FA

C i+1

From

INPR

bit(i)

LD

ADD

DR

INPR

AC(i)

COM

SHR

AC(i+1)

SHL

AC(i-1)

Computer Organization

Computer Architectures Lab

You might also like

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Basic Computer Organization and DesignDocument35 pagesBasic Computer Organization and DesignVinay KumarNo ratings yet

- Basic Computer Organization and DesignDocument35 pagesBasic Computer Organization and Designabhisrit2008No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Slides-Session 7,8 and 9Document40 pagesSlides-Session 7,8 and 9Gabbar SinghNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Basic Computer OrganizationDocument19 pagesBasic Computer OrganizationBarikly RobbyNo ratings yet

- Basic Computer Organization and Design: - Computer Registers - Instruction CycleDocument21 pagesBasic Computer Organization and Design: - Computer Registers - Instruction CycleShashank PandeyNo ratings yet

- Lcdf3 Chap 10 p2Document32 pagesLcdf3 Chap 10 p2Ali Ahmad100% (1)

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- Instruction CodesDocument35 pagesInstruction Codesanilk_patiNo ratings yet

- Memory Reference Instructions ExecutionDocument13 pagesMemory Reference Instructions ExecutionAditya SinghNo ratings yet

- ArchitectureDocument5 pagesArchitectureLove SharmaNo ratings yet

- Basic Computer Organization and DesignDocument46 pagesBasic Computer Organization and DesignKirollos ShawkyNo ratings yet

- Flowchart 16Document4 pagesFlowchart 16amit1650No ratings yet

- Memory Reference InstructionDocument19 pagesMemory Reference InstructionDeepak SinghNo ratings yet

- Introduction to SMIPS ISA Instruction DecodingDocument47 pagesIntroduction to SMIPS ISA Instruction DecodingSai SaurabNo ratings yet

- Basic Computer Organization DesignDocument46 pagesBasic Computer Organization DesignVijaya GoelNo ratings yet

- Basic Computer Organization and DesignDocument42 pagesBasic Computer Organization and DesignSachin MalikNo ratings yet

- Ch7 1Document24 pagesCh7 1Subathra Devi MourouganeNo ratings yet

- Timing and Control Instruction Cycle Memory Reference Instructions Input-Output and Interrupt Complete Computer DescriptionDocument38 pagesTiming and Control Instruction Cycle Memory Reference Instructions Input-Output and Interrupt Complete Computer DescriptionGeorgian ChailNo ratings yet

- Basic Computer ch-5Document48 pagesBasic Computer ch-5Subbu ReddyNo ratings yet

- Chapter 7Document26 pagesChapter 7prachesNo ratings yet

- Unit 7 COADocument24 pagesUnit 7 COAVighnesh SarwankarNo ratings yet

- Solve Problem in Armchair.Document6 pagesSolve Problem in Armchair.r-helouNo ratings yet

- Computer Organization and Design Module III: Instruction Codes, Registers, Memory InstructionsDocument21 pagesComputer Organization and Design Module III: Instruction Codes, Registers, Memory Instructionsvamsi krishna ramavarupuNo ratings yet

- Computer Architecture - Chapt 5Document45 pagesComputer Architecture - Chapt 5for_booksNo ratings yet

- Unit 5a - CPU DesignDocument64 pagesUnit 5a - CPU DesignMʌŋı ßʌķŞhı100% (1)

- Chap. 5 Basic Computer Org. and Design: 5-1 Instruction CodesDocument21 pagesChap. 5 Basic Computer Org. and Design: 5-1 Instruction CodesSisay ADNo ratings yet

- Techniques D'optimisation ArchitecturaleDocument109 pagesTechniques D'optimisation Architecturalesameer_m_daniNo ratings yet

- 03 Bagian 1 Arsitektur AVRDocument22 pages03 Bagian 1 Arsitektur AVRTito Adi NugrohoNo ratings yet

- Cs/Coe 1541: Single and Multi-Cycle ImplementationsDocument93 pagesCs/Coe 1541: Single and Multi-Cycle ImplementationsBobo JooNo ratings yet

- CA SolutionDocument14 pagesCA SolutionSaba InamNo ratings yet

- Miroprogram Control UnitDocument21 pagesMiroprogram Control UnitSameer SalamNo ratings yet

- 03 Sap 1Document30 pages03 Sap 1Joshua Ocariza DingdingNo ratings yet

- Processor Design Single Cycle Processor: Hung-Wei TsengDocument20 pagesProcessor Design Single Cycle Processor: Hung-Wei Tsengwraith324No ratings yet

- Computer Instructions and Control Unit GuideDocument19 pagesComputer Instructions and Control Unit GuideObsii ChalaNo ratings yet

- System Software and Machine Architecture: Department of Computer Science National Tsing Hua UniversityDocument31 pagesSystem Software and Machine Architecture: Department of Computer Science National Tsing Hua UniversitymonajosephjustinNo ratings yet

- Basic Computer OrganisationDocument83 pagesBasic Computer OrganisationMushahid HussainNo ratings yet

- Computer Architecture MIPS Processor DescriptionDocument41 pagesComputer Architecture MIPS Processor DescriptionAsif HussainNo ratings yet

- Computer Architecture: CSCE 350Document41 pagesComputer Architecture: CSCE 350kherberosNo ratings yet

- Cha 1Document31 pagesCha 1Asha NaveenNo ratings yet

- IT18302 - Computer Organization and Architecture Lecture Notes Unit 1-Basic Computer Organization and DesignDocument17 pagesIT18302 - Computer Organization and Architecture Lecture Notes Unit 1-Basic Computer Organization and DesignNAVINRAJ RSNo ratings yet

- Design Contest 2010 MentorDocument27 pagesDesign Contest 2010 MentorUjjwal KantNo ratings yet

- Module 01-MicrocontrollerDocument15 pagesModule 01-MicrocontrollerRejwan TanzinNo ratings yet

- McpuDocument6 pagesMcputpsa6668No ratings yet

- Basic SAP-1 Computer Architecture ExplainedDocument9 pagesBasic SAP-1 Computer Architecture ExplainedAshna100% (1)

- Computer Org Unit 3Document25 pagesComputer Org Unit 3Harshita GopuNo ratings yet

- Week 04Document68 pagesWeek 04aroosa naheedNo ratings yet

- Exam2 ReviewDocument54 pagesExam2 ReviewSurbhie Kalia ChebaNo ratings yet

- ch5 SolDocument9 pagesch5 Solblue_fire_englandNo ratings yet

- D KannanDocument35 pagesD Kannanpreneeth Ramesh007No ratings yet

- Unit 3 CSADocument25 pagesUnit 3 CSAyugdevNo ratings yet

- HW10 11Document3 pagesHW10 11Robert RobinsonNo ratings yet

- GFG - CoaDocument203 pagesGFG - CoaKaran100% (1)

- Asm AsmblerDocument93 pagesAsm AsmblerstormviruxNo ratings yet

- Register Transfer and Micro-Operation Fundamentals ExplainedDocument33 pagesRegister Transfer and Micro-Operation Fundamentals ExplainedSadaf RasheedNo ratings yet

- CH 06Document11 pagesCH 06Sadaf RasheedNo ratings yet

- Central Processing Unit (CPU)Document16 pagesCentral Processing Unit (CPU)Sadaf RasheedNo ratings yet

- Presented By: Syeda Rida Fatima TaqviDocument22 pagesPresented By: Syeda Rida Fatima TaqviSadaf RasheedNo ratings yet

- Chapter 01Document13 pagesChapter 01Sadaf RasheedNo ratings yet

- Solution Manual of Digital Logic and Computer Design (2nd Edition) Morris Mano PDFDocument40 pagesSolution Manual of Digital Logic and Computer Design (2nd Edition) Morris Mano PDFSadaf Rasheed0% (4)

- Data Transfer and Manipulation Instruction GuideDocument16 pagesData Transfer and Manipulation Instruction GuideSadaf RasheedNo ratings yet

- Instruction CycleDocument12 pagesInstruction CycleSadaf RasheedNo ratings yet

- Stack OrganizationDocument6 pagesStack OrganizationSadaf RasheedNo ratings yet

- CH 05Document11 pagesCH 05Samsul ArifinNo ratings yet

- CH 8Document6 pagesCH 8Mustafa JumaNo ratings yet

- 23-Entity-Relationship Data Model - Constraints-Mapping Cardinalities - DBMS Tutorials FoDocument3 pages23-Entity-Relationship Data Model - Constraints-Mapping Cardinalities - DBMS Tutorials FoSadaf RasheedNo ratings yet

- Computer Instruction FormatsDocument12 pagesComputer Instruction FormatsSadaf RasheedNo ratings yet

- 01-Introduction To DBMS-DBMS Tutorials For Beginners in HIndiDocument2 pages01-Introduction To DBMS-DBMS Tutorials For Beginners in HIndiSadaf RasheedNo ratings yet

- Job AnalysisDocument40 pagesJob AnalysisSadaf RasheedNo ratings yet

- RDBMS Concepts Basics Interview Questions PDFDocument6 pagesRDBMS Concepts Basics Interview Questions PDFSadaf RasheedNo ratings yet

- 07-OverView of Data Models-Entity Relationship Model-DBMS Tutorials For Beginners in HindiDocument1 page07-OverView of Data Models-Entity Relationship Model-DBMS Tutorials For Beginners in HindiSadaf RasheedNo ratings yet

- DBMS MCQDocument8 pagesDBMS MCQbenaminsan67% (6)

- 02-Properties of DataBase Part-1-DBMS Tutorials For Beginners in HindiDocument3 pages02-Properties of DataBase Part-1-DBMS Tutorials For Beginners in HindiSadaf RasheedNo ratings yet

- 08-OverView of Data Models-Relational Data Model-DBMS Tutorials For Beginners in Hindi PDFDocument3 pages08-OverView of Data Models-Relational Data Model-DBMS Tutorials For Beginners in Hindi PDFSadaf RasheedNo ratings yet

- 24-Entity-Relationship Data Model-Data Integrity & Keys - DBMS Tutorials For Beginners in HindiDocument2 pages24-Entity-Relationship Data Model-Data Integrity & Keys - DBMS Tutorials For Beginners in HindiSadaf RasheedNo ratings yet

- 25-Entity-Relationship Data Model-RelationShip Sets Keys - DBMS Tutorials For Beginners in HindiDocument2 pages25-Entity-Relationship Data Model-RelationShip Sets Keys - DBMS Tutorials For Beginners in HindiSadaf RasheedNo ratings yet

- 08-OverView of Data Models-Relational Data Model-DBMS Tutorials For Beginners in Hindi PDFDocument3 pages08-OverView of Data Models-Relational Data Model-DBMS Tutorials For Beginners in Hindi PDFSadaf RasheedNo ratings yet

- 27-Entity-Relationship Data Model-Entity-E-R - Diagram To Tables - Rules For Reduction - DBMS Tutorials For Beginners in HindiDocument3 pages27-Entity-Relationship Data Model-Entity-E-R - Diagram To Tables - Rules For Reduction - DBMS Tutorials For Beginners in HindiSadaf RasheedNo ratings yet

- 09-OverView of Data Models-Object Oriented Data MOdel-DBMS Tutorials For Beginners in HindiDocument2 pages09-OverView of Data Models-Object Oriented Data MOdel-DBMS Tutorials For Beginners in HindiSadaf RasheedNo ratings yet

- Data Models: Answers To Review QuestionsDocument13 pagesData Models: Answers To Review QuestionsRosh SibalNo ratings yet

- 04-Various Views of Data-Data Abstraction-DBMS Tutorials For Beginners in HindiDocument4 pages04-Various Views of Data-Data Abstraction-DBMS Tutorials For Beginners in HindiSadaf RasheedNo ratings yet

- Computer Architecture 3rd Edition by Moris Mano CH 06Document22 pagesComputer Architecture 3rd Edition by Moris Mano CH 06Sadaf RasheedNo ratings yet

- Computer Architecture 3rd Edition by Moris Mano CH 08Document43 pagesComputer Architecture 3rd Edition by Moris Mano CH 08Sadaf RasheedNo ratings yet

- Computer Architecture 3rd Edition by Moris Mano CH 07Document24 pagesComputer Architecture 3rd Edition by Moris Mano CH 07Sadaf RasheedNo ratings yet

- Practice Problems For Hardware EngineersDocument177 pagesPractice Problems For Hardware Engineersdon benenoNo ratings yet

- 1 - Memory Unit - Flip-Flops (DLP-2021-22)Document15 pages1 - Memory Unit - Flip-Flops (DLP-2021-22)SohneaNo ratings yet

- Cs2252 Microprocessors and Microcontrollers Question BankDocument2 pagesCs2252 Microprocessors and Microcontrollers Question BankCSETUBENo ratings yet

- Data Path Computer OrganizationDocument11 pagesData Path Computer OrganizationWINORLOSENo ratings yet

- Fabrication, Packaging, and Testing: Chapter 1 IntroductionDocument1 pageFabrication, Packaging, and Testing: Chapter 1 IntroductionCarlos SaavedraNo ratings yet

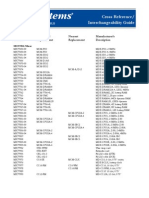

- Cross ReferenceDocument4 pagesCross ReferenceNinjaboy SagaNo ratings yet

- Intersil Space ProductsDocument15 pagesIntersil Space ProductsYze Shiuan YNo ratings yet

- CBM3088 ChipsbankDocument14 pagesCBM3088 ChipsbankBruno StolzNo ratings yet

- BITS Pilani: Digital Signal ProcessingDocument14 pagesBITS Pilani: Digital Signal ProcessingNirneya GuptaNo ratings yet

- EE-307 Fpga Based System Design: Lecture # 02Document35 pagesEE-307 Fpga Based System Design: Lecture # 02Muhammad AnasNo ratings yet

- Processing of Integrated Circuits: Review QuestionsDocument9 pagesProcessing of Integrated Circuits: Review QuestionsEduardo Meléndez SánchezNo ratings yet

- Interfacing Esp8266 With ArduinoDocument13 pagesInterfacing Esp8266 With ArduinoALNATRON GROUPSNo ratings yet

- 8255 Programmable Peripheral InterfaceDocument11 pages8255 Programmable Peripheral Interfacesukantho sikderNo ratings yet

- 99 Digital Electronics Chap10 Lecture 1 BJTDocument32 pages99 Digital Electronics Chap10 Lecture 1 BJTRajesh NelavalaNo ratings yet

- The 8085 and 8086 MicroprocessorsDocument11 pagesThe 8085 and 8086 MicroprocessorsPaayal SasiNo ratings yet

- Lab Initialization, GPIO, Basic SchedulingDocument6 pagesLab Initialization, GPIO, Basic Schedulingmasood ahmadNo ratings yet

- Quiz 1 - System OverviewDocument3 pagesQuiz 1 - System OverviewSahy SahNo ratings yet

- Interrupt and Precise Exception: Computer System ArchitectureDocument21 pagesInterrupt and Precise Exception: Computer System Architectureharshpranav13No ratings yet

- MPMC Overall Question BankDocument5 pagesMPMC Overall Question BankLAKSHMINo ratings yet

- Arm Processor ArchitectureDocument84 pagesArm Processor Architecturebhargava PrasadNo ratings yet

- Unit 1Document9 pagesUnit 1Harikrishnan NairNo ratings yet

- Module 2 - Reading5 - ChipsetDocument3 pagesModule 2 - Reading5 - ChipsetChristopher AdvinculaNo ratings yet

- Classification of Embedded Systems Three Types of Embedded Systems AreDocument24 pagesClassification of Embedded Systems Three Types of Embedded Systems Arekartika_krazeNo ratings yet

- SEC1601Document231 pagesSEC1601Chetan GaurkarNo ratings yet

- MM74HC14 Hex Inverting Schmitt Trigger: General Description FeaturesDocument8 pagesMM74HC14 Hex Inverting Schmitt Trigger: General Description Featuresdaniel ortegaNo ratings yet

- 2ad6a430 1637912349895Document51 pages2ad6a430 1637912349895roopshree udaiwalNo ratings yet

- Microprocessor 80286 & Its Comparison With 80186Document4 pagesMicroprocessor 80286 & Its Comparison With 80186ramyarakiNo ratings yet

- PIC18 Microcontroller OverviewDocument80 pagesPIC18 Microcontroller OverviewFurkan KoşdaşNo ratings yet

- OS Worksheet From Past PapersDocument7 pagesOS Worksheet From Past PapersMUHAMMAD RAMZANNo ratings yet

- Microsemi Smartfusion2 IGLOO2 RTG4 Package Mechanical Drawings Datasheet PD3068 V62Document107 pagesMicrosemi Smartfusion2 IGLOO2 RTG4 Package Mechanical Drawings Datasheet PD3068 V62Wisam ShabanNo ratings yet