Professional Documents

Culture Documents

8086 Interrupts (& Macros) : 1 Zelalem Birhanu, Aait

Uploaded by

tesfu zewdu0 ratings0% found this document useful (0 votes)

15 views13 pagesOriginal Title

Lecture_7.pptx

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

15 views13 pages8086 Interrupts (& Macros) : 1 Zelalem Birhanu, Aait

Uploaded by

tesfu zewduCopyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

You are on page 1of 13

Lecture 7

8086 Interrupts

(& Macros)

Zelalem Birhanu, AAiT 1

In this lecture

8086 Interrupts

8086 Assembly Wrap-up

Macros

Zelalem Birhanu, AAiT 2

Interrupt

Breaks the normal sequence of execution of

instructions and diverts CPU execution to some

other program called Interrupt Service Routine

(ISR)

At the end of each instruction cycle, 8086

checks to see if any interrupts have been

requested

If interrupt is requested, the processor branches

to the ISR, executes the routine and transfers

control back to the main program

Zelalem Birhanu, AAiT 3

8086 Interrupt Types

Two types of interrupts in 8086:

Hardware (External) interrupts

Non-Maskable interrupt (NMI)

o Edge triggered on a LOW to HIGH transition on pin NMI of 8086

Maskable interrupt (INTR)

o High level-triggered on pin INTR of 8086

o Can be masked by resetting IF (Interrupt flag)

(if IF is zero this interrupt is disabled)

Software (Internal) interrupts

Divide by zero, overflow

Interrupts initiated by INT instruction

Zelalem Birhanu, AAiT 4

8086 Interrupt Types cntd

All interrupts (external or internal) can be

initiated by the INT instruction

INT instruction takes an 8 bit operand (type),

therefore 8086 supports up to 256 different

interrupt types

e.g. INT 0 is equivalent to divide by zero

interrupt

INT 2 is equivalent to NMI

Memory locations 00000H to 003FFH are

reserved for interrupt operations

Zelalem Birhanu, AAiT 5

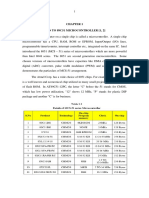

8086 Interrupt Typescntd

3FF TYPE 255

H INTERRUPT

3FC (Available)

H . Four bytes are reserved

. for each type of interrupt

. These bytes specify the

10H TYPE 3 address of the ISR for the

INTERRUPT

(Break Point)

interrupt (2 bytes for

0CH TYPE 2 segment address & 2

INTERRUPT

(NMI)1 bytes for offset address)

08H TYPE

INTERRUPT

04H (Single-step)

TYPE 0

INTERRUPT

00H (Divide by zero)

8086 Interrupt Vector

Table

Zelalem Birhanu, AAiT 6

Interrupt Cycle

The following sequence of actions take place when

CPU acknowledges an interrupt

Flag register is pushed into stack

The IF flag is cleared (to disable INTR interrupt)

The TF (Trap Flag) is cleared (to disable Single-Step

interrupt)

CS register is pushed into stack

IP register is incremented by 2 and pushed into stack

Address of ISR is loaded to CS and IP

An IRET instruction at the end of the ISR returns

execution to the main program

Zelalem Birhanu, AAiT 7

Interrupt Cyclecntd

Zelalem Birhanu, AAiT 8

Interupt Priority

What happens if two or more interrupts occur at

the same time?

The highest-priority interrupt is serviced first then the

next highest priority interrupt is serviced and so on

Interrupt Priority

Divide by zero, INT Highest

n, INTO

NMI

INTR

Single-step Lowest

Zelalem Birhanu, AAiT 9

Interrupt Example

INT 21h can be used for I/O operations in MS-DOS

systems

e.g. 1 The following instructions can be used to read a

character from keyboard

MOV ah, 01

INT 21h ; wait for character input from keyboard

e.g. 2 The following instructions can be used to display a

string on a monitor

LEA dx, str1 ; load starting add. of str1 on dx

MOV ah, 09

INT 21h

str1 db This is a string.$ ; define string

Zelalem Birhanu, AAiT 10

8086 Assembly - Macros

A macro is a short hand for a sequence of other

statements (Instructions, directives, even other macros)

Syntax:

Name MACRO [variable(s)]

assembly statements

ENDM

e.g. A macro to convert ASCII to integer

atoi MACRO number

MOV al, number

AND al, 0Fh

MOV number, al

ENDM

Zelalem Birhanu, AAiT 11

8086 Assembly - Macroscntd

atoi macro num

mov al,num

e.g. and al,0fh

mov num,al org 100h

endm

lea dx,str1

org 100h mov ah,9

int 21h

lea dx,str1 mov ah,1

mov ah,9 int 21h

int 21h mov bl,al

mov ah,1 mov al,bl

int 21h and al,0fh

mov bl,al mov bl,al

atoi bl ret

str1 db "enter number:

ret $"

str1 db "enter number:

$"

Zelalem Birhanu, AAiT 12

More Readings

1. Dr. Manojs Handouts, Chapter 2

2. 8086 datasheet

3. emu8086 documentation

Zelalem Birhanu, AAiT 13

You might also like

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- 8086 Interrupts (& Macros) : 1 Zelalem Birhanu, AaitDocument13 pages8086 Interrupts (& Macros) : 1 Zelalem Birhanu, AaitfikaduNo ratings yet

- A 8051 7 MCS 51中斷結構Document46 pagesA 8051 7 MCS 51中斷結構Brian Yeh100% (1)

- Lesson I Interrupts 8086Document16 pagesLesson I Interrupts 8086VamsiNo ratings yet

- Advanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. PDocument46 pagesAdvanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. Pvishu212167% (3)

- Microprocessors and Interfacing TechniquesDocument23 pagesMicroprocessors and Interfacing TechniquesMuhammad Bilal khanNo ratings yet

- "8086 Interrupts" in (Microprocessor Systems and Interfacing)Document20 pages"8086 Interrupts" in (Microprocessor Systems and Interfacing)MUHAMMAD ABDULLAHNo ratings yet

- Interrupt Structure and Processing of 8086Document16 pagesInterrupt Structure and Processing of 8086kpenchal615No ratings yet

- Interrupt 8086Document24 pagesInterrupt 8086Aarti KushwahaNo ratings yet

- Interrupts PDFDocument5 pagesInterrupts PDFPraveen Kumar ReddyNo ratings yet

- 8086 Microprocessor InterruptsDocument27 pages8086 Microprocessor InterruptsABRAR RASUL QADRINo ratings yet

- 8051 Interrupts: 1 Interrupt SourcesDocument5 pages8051 Interrupts: 1 Interrupt SourcescrsarinNo ratings yet

- Mci Unit-2Document17 pagesMci Unit-2Muni Sankar MatamNo ratings yet

- CH 8Document13 pagesCH 8Gcross NGNo ratings yet

- Unit 3 MicroprocessorsDocument61 pagesUnit 3 Microprocessors076 Sadaf Aalia KhanNo ratings yet

- 3 Interrupts and Interrupt Service Routines: 3.1 What Is An Interrupt?Document11 pages3 Interrupts and Interrupt Service Routines: 3.1 What Is An Interrupt?Khalifa EltayebNo ratings yet

- Interrupt Interface of The 8088 and 8086 MicroprocessorDocument32 pagesInterrupt Interface of The 8088 and 8086 Microprocessorkaram hayderNo ratings yet

- 8051 InterruptDocument21 pages8051 InterruptarunvittoNo ratings yet

- CSULB - CECS 285 - Chapter Eleven Fall 2010 - R.W. Allison 1Document17 pagesCSULB - CECS 285 - Chapter Eleven Fall 2010 - R.W. Allison 1Lavanya MeenakshisundaramNo ratings yet

- 8 8086 InterruptsDocument26 pages8 8086 InterruptsAnshuman MitraNo ratings yet

- 8085 Interrupts: Enabling, Disabling and StepsDocument7 pages8085 Interrupts: Enabling, Disabling and StepsDonika MarkandeNo ratings yet

- 8051 InterruptsDocument3 pages8051 Interruptsbt21me011No ratings yet

- Interrupts in 8051: Microprocessor Laboratory EE-337Document11 pagesInterrupts in 8051: Microprocessor Laboratory EE-337Ayandev BarmanNo ratings yet

- 8086 Interrupt Vector TableDocument13 pages8086 Interrupt Vector TableLim Yee FattNo ratings yet

- Interrupts: Lec Note 8Document22 pagesInterrupts: Lec Note 8Rayan IsranNo ratings yet

- Module - III (A&B)Document80 pagesModule - III (A&B)PamusainagaharshavardhanNo ratings yet

- 2 Advanced+MicroprocesorDocument66 pages2 Advanced+MicroprocesorMilind KhanderaoNo ratings yet

- Module III Interrupts in 8086: Types, NMI, INTR, ISRDocument19 pagesModule III Interrupts in 8086: Types, NMI, INTR, ISRSagar ChaulagaiNo ratings yet

- Interrupts PDFDocument4 pagesInterrupts PDFHermain Fayyaz KarimNo ratings yet

- 8086 InterruptsDocument24 pages8086 InterruptsAshwini ManojNo ratings yet

- Lec_11_MSI_InterruptsDocument21 pagesLec_11_MSI_InterruptsAhsanNo ratings yet

- 8086 Interrupts: InterruptDocument5 pages8086 Interrupts: InterruptN.RAMAKUMARNo ratings yet

- Last Experiment MicroDocument11 pagesLast Experiment MicroRuth DVNo ratings yet

- Iii Unit Mpi Part ADocument5 pagesIii Unit Mpi Part AN.RAMAKUMARNo ratings yet

- MC Unit 1Document14 pagesMC Unit 1sureshgurujiNo ratings yet

- Pic18 Interrupt 2Document19 pagesPic18 Interrupt 2adamwaiz100% (3)

- Interrupts: RST 7.5 RST 6.5 RST 5.5 1 Non-Vectored Intr 1 Non-Maskable Vectored TrapDocument11 pagesInterrupts: RST 7.5 RST 6.5 RST 5.5 1 Non-Vectored Intr 1 Non-Maskable Vectored TrapHamza Abu AjamiaNo ratings yet

- 8051 InterruptsDocument35 pages8051 InterruptsSoma Bharath Kumar ReddyNo ratings yet

- Hardware & Software InterruptsDocument33 pagesHardware & Software InterruptsShubham BakshiNo ratings yet

- Ch13 InterruptDocument41 pagesCh13 InterruptMir4 BritoNo ratings yet

- 80x86 InterruptsDocument33 pages80x86 InterruptsVIVEK K PNo ratings yet

- The 8051 Microcontroller and Embedded Systems: Interrupts Programming in AssemblyDocument26 pagesThe 8051 Microcontroller and Embedded Systems: Interrupts Programming in AssemblyAnushkaSinhaNo ratings yet

- Interfacing With Advanced DevicesDocument76 pagesInterfacing With Advanced DevicesSai Krishna KodaliNo ratings yet

- 8051 Interrupts: Enable, Disable Serial, Timer 0, External Hardware InterruptsDocument32 pages8051 Interrupts: Enable, Disable Serial, Timer 0, External Hardware InterruptsBRO CUBIESNo ratings yet

- Interrupts in 8086Document4 pagesInterrupts in 8086Radhakrishna100% (1)

- Microprocessors InterruptsDocument51 pagesMicroprocessors InterruptsLHKNo ratings yet

- InterruptsDocument43 pagesInterruptsapi-19970915No ratings yet

- CS601: Microprocessor & Interfacing: UNIT 1: 05/03/2010 1 Arvind ShrivastavaDocument23 pagesCS601: Microprocessor & Interfacing: UNIT 1: 05/03/2010 1 Arvind ShrivastavaArvind ShrivastavaNo ratings yet

- Microprocessor Systems Lab Experiment 4 BodyDocument6 pagesMicroprocessor Systems Lab Experiment 4 BodyRuth Abegail de VeraNo ratings yet

- 8086 Interrupt Processing and Interrupt Vector TableDocument16 pages8086 Interrupt Processing and Interrupt Vector TableDarshan BysaniNo ratings yet

- 2150907Document14 pages2150907Prashant ShahNo ratings yet

- Interrupt in 8085 Micro-Processor ExplainedDocument15 pagesInterrupt in 8085 Micro-Processor ExplainedMedo KassabNo ratings yet

- Interrupts Part 1Document14 pagesInterrupts Part 1leemong335No ratings yet

- InterruptsDocument13 pagesInterruptsJasleen KaurNo ratings yet

- Lab5 Interupt 8051 2023Document8 pagesLab5 Interupt 8051 2023k12onlinenroNo ratings yet

- 08 - Chapter 1 PDFDocument47 pages08 - Chapter 1 PDFMalcolm DopaimNo ratings yet

- Software and Hardware Interrupt ApplicationsDocument10 pagesSoftware and Hardware Interrupt Applicationssatyanarayana12No ratings yet

- 8051 SlidesDocument42 pages8051 SlidesRituparnaNo ratings yet

- Amp Module 2Document15 pagesAmp Module 2fasnamditNo ratings yet

- EEE 412 Part-4-InterruptDocument8 pagesEEE 412 Part-4-InterruptvictorNo ratings yet

- 5th Yr CH 1 and 2newDocument17 pages5th Yr CH 1 and 2newtesfu zewduNo ratings yet

- Lab 1Document1 pageLab 1tesfu zewduNo ratings yet

- Lecture Note - Top Level View of ComputerDocument6 pagesLecture Note - Top Level View of Computertesfu zewduNo ratings yet

- Lecture Note For OSDocument8 pagesLecture Note For OStesfu zewduNo ratings yet

- FOCA Chapter 1Document18 pagesFOCA Chapter 1Balaji RajendranNo ratings yet

- QuestonsDocument2 pagesQuestonstesfu zewdu0% (1)

- The 8086 Microprocessor Architecture: (Register Level Organization)Document31 pagesThe 8086 Microprocessor Architecture: (Register Level Organization)tesfu zewduNo ratings yet

- Lecture05 - 8086 AssemblyDocument43 pagesLecture05 - 8086 Assemblytesfu zewduNo ratings yet

- Lecture01 PDFDocument23 pagesLecture01 PDFtesfu zewduNo ratings yet

- QuestonsDocument2 pagesQuestonstesfu zewdu0% (1)

- Lecture 9Document17 pagesLecture 9tesfu zewduNo ratings yet

- Hardwired and Microprogrammed Control2Document4 pagesHardwired and Microprogrammed Control2adddataNo ratings yet

- Lecture 5Document21 pagesLecture 5tesfu zewduNo ratings yet

- The 8086 Microprocessor Architecture: (Register Level Organization)Document31 pagesThe 8086 Microprocessor Architecture: (Register Level Organization)tesfu zewduNo ratings yet

- Assembly Language Overview and ExampleDocument22 pagesAssembly Language Overview and Exampletesfu zewduNo ratings yet

- Lecture 1Document14 pagesLecture 1tesfu zewduNo ratings yet

- Microprocessor Interfacing Fundamentals ExplainedDocument56 pagesMicroprocessor Interfacing Fundamentals Explainedtesfu zewduNo ratings yet

- Ch3 PDFDocument62 pagesCh3 PDFtesfu zewduNo ratings yet

- Ch1 PDFDocument16 pagesCh1 PDFtesfu zewduNo ratings yet

- Lecture03 PDFDocument30 pagesLecture03 PDFtesfu zewduNo ratings yet

- Lecture01 IntroDocument30 pagesLecture01 Introtesfu zewduNo ratings yet

- Ch2 PDFDocument53 pagesCh2 PDFtesfu zewduNo ratings yet

- Lecture01 PDFDocument23 pagesLecture01 PDFtesfu zewduNo ratings yet

- Microprocessor Fabrication Trends and Prospects: (Cont'd)Document3 pagesMicroprocessor Fabrication Trends and Prospects: (Cont'd)tesfu zewduNo ratings yet

- ct3200 Digitalacts PDFDocument46 pagesct3200 Digitalacts PDFtesfu zewduNo ratings yet

- Java Worksht+exer PDFDocument12 pagesJava Worksht+exer PDFtesfu zewduNo ratings yet

- MicroProcessor SyllabusDocument8 pagesMicroProcessor Syllabustesfu zewduNo ratings yet

- 8086 RegistersDocument3 pages8086 RegistersjerryNo ratings yet

- Processor ArchitechorDocument12 pagesProcessor ArchitechorAbhijit BeheraNo ratings yet

- Code of Conduct at Pizza HutDocument2 pagesCode of Conduct at Pizza HutAdeel Chaudhary0% (1)

- Gta Namaste America Cheat CodesDocument4 pagesGta Namaste America Cheat CodesGaurav PathakNo ratings yet

- Environmental Science Course Project-1Document27 pagesEnvironmental Science Course Project-1vaishnaviNo ratings yet

- Threadmilling Brochure SecoDocument16 pagesThreadmilling Brochure SecoIvica LabudovicNo ratings yet

- C Programming: Charudatt KadolkarDocument34 pagesC Programming: Charudatt KadolkarDhiliban SwaminathanNo ratings yet

- Adding Value To Corporate Recruitment: Carlos Jordán de Urries Talent Search ConsultantDocument8 pagesAdding Value To Corporate Recruitment: Carlos Jordán de Urries Talent Search ConsultantCarlos Jordan de UrriesNo ratings yet

- Mistika SGCDocument17 pagesMistika SGCflameadgNo ratings yet

- L .. Eee - .: Distribution Voltage RegulatorsDocument11 pagesL .. Eee - .: Distribution Voltage RegulatorsSirajulNo ratings yet

- To Civil Engineering: RoadsDocument30 pagesTo Civil Engineering: Roadshemant kumarNo ratings yet

- MELHORES SITES DE INFOPRODUTOS PLR E SUAS RANKS NO ALEXADocument8 pagesMELHORES SITES DE INFOPRODUTOS PLR E SUAS RANKS NO ALEXAAlexandre Silva100% (2)

- Slabs Are Plate Elements Forming Floors andDocument5 pagesSlabs Are Plate Elements Forming Floors andyasas89No ratings yet

- Basic Functions of A Computer SystemDocument3 pagesBasic Functions of A Computer SystemAlanlovely Arazaampong AmosNo ratings yet

- How To Use AZUpDocument1 pageHow To Use AZUpjovicasNo ratings yet

- Machine TimeDocument11 pagesMachine TimeFRANCIS THOMASNo ratings yet

- Hole Cleaning PDFDocument68 pagesHole Cleaning PDFHarold AldayNo ratings yet

- Technology in Supply Chain ManagementDocument8 pagesTechnology in Supply Chain ManagementjasmineNo ratings yet

- User Home - MoneyEasilyDocument1 pageUser Home - MoneyEasilyEbenezer NyantakyiNo ratings yet

- Dual-Band Band Pass Filters Using Stub-Loaded ResonatorsDocument3 pagesDual-Band Band Pass Filters Using Stub-Loaded ResonatorsfracosoeNo ratings yet

- VAHAN SERVICE - User ManualDocument30 pagesVAHAN SERVICE - User ManualGURBACHAN SINGH ChouhanNo ratings yet

- PBV20N2 Service Manual PDFDocument244 pagesPBV20N2 Service Manual PDFJack Norhy100% (1)

- Kurzweil MicropianoDocument24 pagesKurzweil Micropianoestereo8No ratings yet

- Restaurant Pub VIP Lounge Camp Pune SaleDocument4 pagesRestaurant Pub VIP Lounge Camp Pune SaleChandrashekhar Naikare0% (1)

- Nmo & DmoDocument29 pagesNmo & DmoJessica Julien100% (1)

- 6.unit I 2 MarksDocument3 pages6.unit I 2 MarksprasanthprpNo ratings yet

- HDDTB 15 PDFDocument4 pagesHDDTB 15 PDFdakidofdaboomNo ratings yet

- Dse7110 Mkii Dse7120 Mkii Operator ManualDocument100 pagesDse7110 Mkii Dse7120 Mkii Operator Manualseanfsmyth100% (1)

- Solids Flow Feeder Equipment for Precise Measurement & ControlDocument7 pagesSolids Flow Feeder Equipment for Precise Measurement & ControlAbhishek DuttaNo ratings yet

- Blackberry Enterprise Server For Microsoft Exchange: Troubleshooting GuideDocument48 pagesBlackberry Enterprise Server For Microsoft Exchange: Troubleshooting GuideKhaled AjouzNo ratings yet

- IQ3-95SP-BC dimensional data sheetDocument2 pagesIQ3-95SP-BC dimensional data sheetren kaiNo ratings yet

- Range and Angle Tracking Techniques for Moving Target EstimationDocument34 pagesRange and Angle Tracking Techniques for Moving Target Estimationmykingboody2156No ratings yet